Capability-Based Memory Protection for Scalable Vector Processing

Submitted for Advanced Computer Science MPhil @ University of Cambridge, 2022

Winner of the RISE 2022 Student Competition!

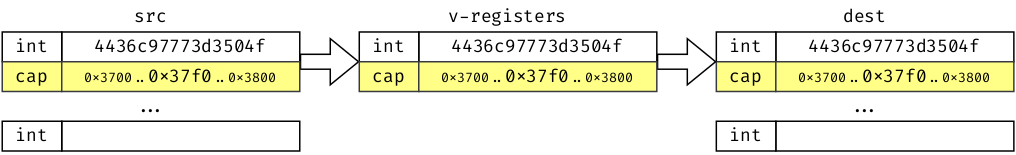

My master’s project examines the impact of combining CHERI’s hardware memory protection with vector processing, particularly vectorized loads and stores, by designing a potential specification for “CHERI-RVV” - a CHERI version of the RISC-V “V” scalable vector extension.

Artefacts

- Dissertation (pdf)

- Summary (blogpost)

- CHERI-RVV hardware emulator and test programs (docs)

- Rust wrapper for the

cheri-compressed-capC library (docs) - CHERI-Clang fork, with CHERI-RVV support

Presentations

- End-of-year presentation (pdf)

- RISE competition presentation (youtube, embedded above)

Recommended citation

Stark, Samuel W. (2022). Capability-Based Memory Protection for Scalable Vector Processing. [MPhil thesis]. University of Cambridge. URL: https://theturboturnip.com/files/2022-06-06-capability-protection-scalable-vectors.pdf

@mastersthesis{starkCapabilityProtectionScalableVectors2022,

author = "Stark, Samuel W.",

title = "Capability-Based Memory Protection for Scalable Vector Processing",

school = "University of Cambridge",

year = "2022",

month = "June",

url = "https://theturboturnip.com/files/2022-06-06-capability-protection-scalable-vectors.pdf"

}